Five-Minute Tutorial: EM Model Files Revisited

11 Things I Learned by Browsing Cadence Online Support

I guess by now most of us are already familiar with Rapid Adoption Kits (RAKs). These are packages that include a detailed instructional document and a lab database. You can browse all the available materials at http://support.cadence.com.

Rapid Adoption Kits (RAKs) - The purpose of RAKs is to demonstrate how users can use Cadence tools in their design flows to improve productivity and to maximize the benefits of their tools. Here are a few important RAKs and appnotes that were published recently on the support portal (http://support.cadence.com) which might be of interest to many of us!

1. RAK - Prototyping Foundation Flat Flow EDI 13.2This content helps us learn gigascale prototyping with FlexModels and presents a prototyping usage model. FlexModels enable gigascale design exploration using the Encounter Digital Implementation (EDI) System.

2. RAK - Introduction to EDI System 13.2 & Block Implementation Flow

This RAK can be extremely helpful for beginners who intend to learn the EDI System. RAK includes EDI command and graphical user interface (GUI), how to set up the EDI system, and how to implement the flat flow that can be used for chip or block Implementation

3. RAK - Basic Floorplanning in EDI System 13.2

This knowledge piece helps us learn how to specify the floorplan, move and edit placement constraints, create placement and routing blockages, create power and ground rings and stripes, and power routing

4. RAK - Power and Rail Analysis Using Encounter Power System (EPS) 13.1

This material provides information on to know how to do library characterization, analyze VCD files for windows of high signal activity, do static and dynamic power analysis, analyze current/power plots, perform what-if analysis & analyze various rail analysis plots

5. Appnote - Time Budgeting for Very Large, Timing Critical Hierarchical Design Using ART Methodology

Time budgeting for very large timing-critical designs using virtual optimization is not accurate enough. With design sizes growing to over 300 million instances, obtaining accurate time budgets with better accuracy for timing critical design is becoming a necessity for many design teams. This document crisply describes how to obtain accurate time budgets using Active-Logic Reduction Technology (ART) to reduce run-time and memory footprint on timing critical designs. This should help the user achieve accurate timing budgets.

6. Appnote - Constraint Implementation and Validation in Interoperability Flow

The key benefit designers derive by using a mixed signal Interoperability flow and OpenAccess (OA) database is the seamless transfer and implementation of various routing constraints from analog to digital designs. Starting from Encounter Digital Implementation (EDI) 13.2 and Virtuoso 616, it is not only simple to create these constraints, but it is also easy to import or export them from one environment to another. Once the design is implemented using these constraints, you can use the Physical Verification System-Constraint Validation (PVS-CV) utility to validate whether these constraints are implemented correctly.

7. Appnote - Context Aware Placement in EDI SystemThis document is targeted to users who want to apply context constraint for cells with Encounter Digital Implementation System (EDI System). It will introduce how to define edge types and the requested spacing rules, how to assign the specified edge types to cells, and how to spread cells with specific edge types to satisfy the spacing rules. It includes recommendations for a successful chip implementation.

8. Appnote - How to Detect and Fix Isolated Cut Via Violations

This content is meant for users and designers needing to locate and fix isolated cut violations in their designs, and CAD engineers wishing to implement such a flow using the Encounter Digital Implementation (EDI) system. This document provides some background to the problem, and a methodology for resolving violations by inserting multi-cut vias.

9. Appnote - Current Mode Virtual Attacker

Modeling small attackers accurately and efficiently is an important factor in the accuracy of noise and noise-on-delay analysis. This application note explains how the current mode virtual attacker is formed and used.

10. Appnote - End Cap Cells Usage in Encounter Digital Implementation (EDI) System FlowIf you want to insert end caps into the design with Encounter Digital Implementation System, this content should help you achieve your goal. It will introduce you to various end cap insertion and verification methodologies recommendations from Cadence for a successful chip implementation.

11. Appnote - Path Exception Priority RulesThis document describes the path exception priority rules which are followed by Encounter Timing System (ETS) / Encounter Digital Implementation (EDI) System for finding effective path exception for a path, among the multiple path exceptions specified for that path. Path exception priority rules are explained (in descending order) as per path exception command type and various command options.

Happy Learning !!

Mukesh Jaiswal

Five-Minute Tutorial: Start the New Year with Voltus

- licensing info

- how to start the tool

- pointers to translation utilities for your existing scripts

- an explanation of the new power grid library view types and how they are used (there used to be 8 different kinds, now there are only 3 - much better!)

- power grid library generation

- static power analysis

- static rail analysis

- dynamic power analysis

- dynamic rail analysis

- vectorless and vector-based analysis

- how to look at results in report files, plots, graphs, etc.

Sharing is Learning - New RAKs and Videos for Digital Users on Cadence Support

Friends, you would probably agree that sharing knowledge is a practical way to solve business problems, and contributes to business goals. Thought I'd share some great content that I came across while navigating through http://support.cadence.com

Rapid Adoption Kits:

Static Timing Analysis using Tempus (Signoff Timing Analysis) 13.2

With the help of this RAK (rapid adoption kit) you will learn how to perform static timing analysis on a dual-tone multi-frequency (DTMF) design using Cadence Tempus Timing Signoff Solution in each of the four modes shown below:

Tempus STA Single Mode Single Corner SMSC

Tempus STA Distributed Multi-Mode Multi-Corner DMMMC

Tempus STA Concurrent Multi-Mode Multi-Corner CMMMC

Tempus DSTA Distributed STA on multiple clients Tempus DSTA

You will be able to:

• Understand how to set up and run each of the Tempus Timing Signoff Solution methods

• Report and analyze static timing results

• Be confident on how to start your new design and choose the methods that are best for you

Timing Signoff Optimization (TSO) using TEMPUS 13.2 & EDI System 13.2

In this RAK, you will learn how to perform ECOs (engineering change orders) for solving hold, setup, and DRV timing violations on a dual-tone multi-frequency (DTMF) design using Tempus Timing Signoff Solution and Cadence Encounter Digital Implementation System.

First section of this will cover Tempus TSO fixing on a block-level design and the subsequent will cover hierarchical chip finishing using Tempus TSO.

This will help to:

• Explain how to investigate timing in an signoff STA environment

• Understand and explain the timing ECO methodology

• Understand and perform all the steps required before starting the ECO process

• Perform hold, setup, and DRV timing fixes through ECOs

• Report and analyze ECO results

• Implement the ECOs in Encounter Digital Implementation System

• Verify final signoff STA

• Assemble a hierarchical design in Tempus Timing Signoff Solution for STA and ECO fixing

• Perform hierarchically aware chip finishing with timing ECOs

• Optimize timing in replicated modules (master/clone)

Videos:

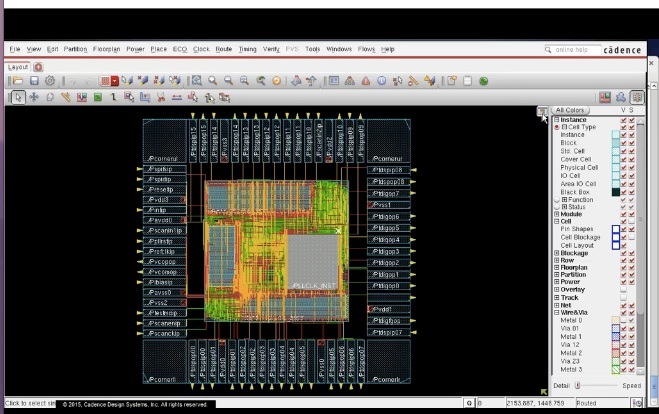

Demo on Implementing Hierarchical Design Using EDI System

This knowledge resource is meant for beginners, new users of EDI System, or users new to the digital implementation design flow. This will help users to learn steps needed in specifying the partitions, creating power and ground rings, running placement and trial/route, assigning partition pins, deriving timing budgets, committing the partitions, pushing into the partitions, and, finally, saving the partitions.

How to create and use ILM (Interface Logic Model) in EDI system

This video showcases steps required in creating the ILMs of a partitioned block, implementation of created ILMs at the top level, and checking of interface logic at the top level of the specified ILM and viewing path, penetrating into the block up to interface logic of the path.

Hope you find these knowledge resources useful.

Happy Learning!

Mukesh Jaiswal

Quick Reference - 8 Ways to Optimize Power Using Encounter Digital Implementation (EDI) System

Everyone knows that the increasing speed and complexity of today's designs implies a significant increase in power consumption, which demands better optimization of your design for power. I am sure lot of us must be scratching our heads over how to achieve this, knowing that manual power optimization would be hopelessly slow and all too likely to contain errors.

Here are 8Top Things you need to know to optimize your design for power using the Encounter Digital Implementation (EDI) System.

Given the importance of power usage of ICs at lower and lower technology nodes, it is necessary to optimize power at various stages in the flow. This blog post will focus on methods that can be used to reach an optimal solution using the EDI System in an automated and clearly defined fashion. It will give clear and concise details on what features are available within optimization, and how to use them to best reach the power goals of the design.

Please read through all of the information below before making a decision on the right approach or strategy to take. It is highly dependent on the priority of low power and what timing, runtime, area and signoff criteria were decided upon in your design. With the aid of some or all of the techniques described in this blog it is possible to, depending on the design, vastly reduce both the leakage and dynamic power consumed by the design.

Quick Reference - Top Things to Know about Power OptimizationAll of the following items discussed here in brief are covered in greater detail in Low Power Optimization in EDI System appnote posted on http://support.cadence.com/

This is a one stop quick reference and not a substitute for reading the full document.

1) VT partition uses various heuristics to gather the cells into a particular partition. Depending on how the cells get placed in a particular bucket, the design leakage can vary a lot. The first thing is to ensure that the leakage power view is correctly specified using the "set_power_analysis_mode -view" command. The "reportVtInstCount -leakage" command is a useful check to see how the cells and libraries are partitioned. Always ensure correct partitioning of cells.

2) In several designs, manually controlling certain leakage libraries in the flow might give much better results than the automated partitioning of cells. If the VT partitioning is not satisfactory, or the optimization flow is found to use more LVT cells than targeted, selectively turn off cells of certain libraries particularly in initial part of the flow i.e. preRoute flow. The user should selectively set the LVT libraries to "don't use" and run preCts/postCts optimization. Depending on final timing QOR, another incremental optimization with LVT cells enabled may be needed.

3) Depending on the importance of leakage/dynamic power in the flow, the leakage/dynamic power flow effort can be set to high or low.

setOptMode -leakagePowerEffort {low|high}

setOptMode -dynamicPowerEffort {low|high}

If timing is the first concern, but having somewhat better leakage/dynamic power is desired, then select low. If leakage/dynamic power is of utmost importance, use high.

4) PostRoute Optimization typically works with all LVT cells enabled. In case of large discrepancy between preRoute and postRoute timings or if SI timing is much worse than base timing, postRoute optimization may overuse LVT cells. So it may be worthwhile experimenting with a two pass optimization, once with LVT cells disabled, and then with LVT cells enabled.

5) In order to do quick PostRoute timing optimization to clean up final violations without doing physical updates, use the following:

setOptMode -allowOnlyCellSwapping true

optDesign -postRoute

This will only do cell swapping to improve timing, without doing physical updates. This is specifically for timing optimization and will worsen leakage.

6) Leakage flows typically have a larger area footprint than non-leakage flows. This is because EDI trades area with power, as it uses more HVT cells to fix timing to reduce leakage. This sometimes necessitates reclaiming any extra area during postRoute Opt to get better convergence in timing. EDI has an option to turn on area reclaim postRoute which is hold aware also and will not degrade hold timing.

setOptMode -postRouteAreaReclaim holdAndSetupAware

7) Running standalone Leakage Optimization to do extra leakage reclamation:

optLeakagePower

This may be needed if some of the settings have changed or if leakage flows are not being used.

8) PreRoute Optimization works with an extra DRC Margin of 0.2 in the flow. On some designs it is known to result in extra optimization causing more runtime and worse leakage. The option below is used to reset this extra margin in DRV fixing:

setOptMode -drcMargin -0.2

Remember to reset this margin for postRoute optimization to 0, as postRoute doesn't work with this extra margin of 0.2. Note that the extra drcMargin is sometimes useful in reducing the SI effects, so by removing the extra margin, more effort may be needed to fix SI later in the flow.

I hope these tips help you achieve your power goals of your designs!

-Mukesh Jaiswal

Five-Minute Tutorial: Create Encounter Power System (EPS) Power-Grid Views For Standard Cells

CDNLive High-Performance Track: Do You Have What it Takes to Get Your High-Performance SoC to Market?

Implementing SoCs with embedded processors at advanced nodes has become increasingly difficult. This is due to the complexity of the design functionality as well as the low power and increased performance requirements driven by a plethora of end-user applications in modern hand-held devices. Path-breaking trends in ARMv8 64-bit processor based microservers for power efficient cloud computing/data centers and high-end content generating superphones and tablets have thrown new curveballs at chip designers. As we're aware, battery technology hasn't kept pace with Moore's Law and as a result some amazing recent advances in process technology (such as FinFET, double patterning, etc.) and EDA tools are helping offset the difficulties in designing power efficient yet high-performance SoCs.

I'm really pleased to see a lineup of exciting papers in the High-Performance Digital Implementation track at the upcoming CDNLive Silicon Valley in Santa Clara, March 12, from some of the heavy hitters in the industry. These presentations describe the implementation of SoCs for a multitude of designs such as ARM Cortex-A core-based applications processors with state-of-the-art GPUs for demanding high-end smartphones and tablets; the world's first multi-Gigahertz ARMv8 64-bit processor architecture based server-on-chip for cloud computing/data centers; and complex networking ASICs, to name a few.

Rounding off the sessions are interesting papers from ARM on implementing their latest 64-bit Cortex-A57 processor based on the ARMv8 architecture and processor optimization pack (POP) IP development for ARM's big.LITTLETM paradigm -- with Cortex-A15 and Cortex-A7 processors respectively -- with Cadence's Encounter digital flows. These presentations exemplify the strong partnership and collaboration between ARM and Cadence in developing implementation reference methodologies (iRM) that ease designing ARM processors into leading-edge SoCs and accelerate time-to-market.

A common thread that the audience will hear is the significant power, performance and area (PPA) improvements customers have been able to achieve with some of the key Cadence tools such as RTL Compiler-Physical (RCP) and Encounter Digital Implementation (EDI) System featuring the latest GigaOpt physical optimization and Clock Concurrent Optimization (CCOpt) technologies. RCP, GigaOpt and CCOpt form the three pillars of Cadence's strong offering for implementing complex and high-performance designs in silicon. Some of the key advances include extending GigaOpt to the entire optimization flow (pre- and post-route) with full multi-CPU support, route-driven and layer-aware optimization at advanced nodes, and native integration of CCOpt in EDI, all leading to significant PPA improvements. Stop by the Cadence booth at the partner expo to learn more about the upcoming EDI release 13.1 highlights!

I've always been fascinated by our customers' end-products and verticals (going beyond just chip design and into adjacencies) where Cadence's tools have been used for bleeding-edge designs. So when companies such as AppliedMicro, ARM, Avago and NVidia come to town to graciously share their design experiences, one can't help but sit up and take notice! CDNLive gives a wonderful opportunity for attendees to understand the intricacies behind implementing these complex SoCs, including the challenges faced-from synthesis, design planning to final implementation, signoff and everything in between-and how they surmounted them. Key takeaways include lessons learned and best practices that the audience can readily deploy into their own designs and methodologies. That's the beauty of CDNLive-it provides ample opportunities to learn from fellow designers while extending one's professional network. What more can you ask for?

On Wednesday, March 13, the R&D luncheon offers a unique opportunity for our customers to sit down with our R&D and product engineers to discuss the chip-design problems of the day. We've set up thematic tables to cater to different areas of focus, including Advanced Node (28/20/16/14nm), Clock Concurrent Optimization, Implementing GHz+ ARM Cortex-A processor based designs, low-power, mixed-signal, signoff, and more! This offers an informal atmosphere for Cadence to also better understand our customers' requirements.

Here's a sneak peek into the paper presentations in the high-performance track on March 12, 2013:

- In Session HP105 (4:45-5:35pm), Sumbal Rafiq of AppliedMicro will present "X-Gene: Realizing a complex high-performance and power efficient 64-bit multicore ARMv8 based server-on-chip solution in silicon". This revolutionary multi-gigahertz design targets the extremely demanding cloud-computing/datacenter market. With multi-core ARMv8 CPUs, network interface controller (NIC), high-speed interconnect fabric, memory and other peripherals, the design complexity has reached unprecedented levels, throwing several new challenges in chip integration and meeting stringent PPA metrics. AppliedMicro and Cadence have collaborated from an early stage of development to deploy an RTL-to-GDSII flow based on Cadence's Encounter Digital tools to successfully implement and tape out the design. The proof's in working silicon!

- Session HP 104 (9:00-9:50am) titled"High Performance/Low Power Implementation of ARM Cortex-A15 and Cortex-A7 with ARM POP IP for ARM big.LITTLE Systems and Applications" will be presented by Sathyanath Subramanian from ARM. Sathya will talk about ARM's big.LITTLE heterogeneous processing concept and how the ARM POP IP optimized with Cadence's flows at advanced nodes provides designers a head start and a PPA boost for implementing designs with Cortex-A15 and Cortex-A7 processors.

- In Session HP103 (2:30-3:20pm), Brent McKanna of ARM will present Targeting High Frequency and Power Efficient Implementations for ARM's High Performance Cortex-A57 Processor. Cortex-A57 is ARM's latest and highest performing ARMv8 64-bit processor targeting the enterprise server and high-end smartphone/tablet applications, where maintaining high power efficiencies at superior performance points are critical. ARM and Cadence have collaborated throughout the development of Cortex-A57 to create an RTL-to-signoff flow based on Cadence Encounter design tools. The paper describes the techniques used for handling the increased complexity of larger ARM cores and for closing designs on advanced nodes such as 28nm.

- Session HP102 (1:30-2:20pm) titled Advanced Strategies for Timing Closure Utilizing New GigaOpt Features will be presented by Jack Benzel of Avago Technologies. Given the explosive growth in the number of large memory macros and the growing dominance of RC delays limiting long-haul wire performance at advanced nodes, new strategies are required to address low-latency architectures. Jack's paper will cover several of EDI System's new GigaOpt features including low-RC layer promotion, advanced re-buffering, TNS focus, path balancing, and path compaction. Get exposed to real-world 28nm examples demonstrating before/after QOR improvements.

- In Session HP101 (3:45-4:35pm), Santosh Navale of NVidia will present Implementing high performance GHz+ mobile applications processors and GPU with clock concurrent design techniques. Hear about how NVidia changed their clocking methodology to tackle several hundred complex generated and interacting clock signals, which form the back-bone of modern applications processors. Hear how they handled on-chip-variation, complex clock gating, multi-mode/multi-corner, and low-power requirements while improving chip performance with the Cadence clock concurrent optimization (CCOpt) technology on multi-Gigahertz ARM CPU based mobile applications and GeForce GPU processors.

Registration and program information for CDNLive Silicon Valley is available here.

Vasu Madabushi

Five-Minute Tutorial: Set Flip-Chip Bumps as Voltage Sources in EPS/EDI Rail Analysis

When running power and rail analysis for a flip chip, we used to have to spend some time creating the voltage sources. It wasn't too terrible; usually we would output the bumps into a Cadence Encounter Digital Implementation (EDI) .io file, then use a perl script to filter out the pwr/gnd bumps and create the voltage source file format. The script would need a bit of editing from project to project, but nothing too complicated. We ended up with a voltage source file, with one point-source per bump. However, it is much easier these days to create voltage sources for a flip chip to be used in the Cadence Encounter Power System (EPS) Rail Analysis (run either from EPS directly, or through EDI.) It is also more accurate, since the bumps get modeled with several points in a resistor network. (This will avoid false EM violations.)

The LEF file of your flip chip bump will be used as a reference. Bumps are usually octagonal, although sometimes are represented as squares. Here is an example bump LEF, which I will use to illustrate the process. (Note that a polygon shape is used to create an octagonal bump, but the corresponding coordinates that would have been used for a square are commented out.)

VERSION 5.6 ;

BUSBITCHARS "[]" ;

DIVIDERCHAR "/" ;

UNITS

DATABASE MICRONS 1000 ;

END UNITSMACRO BUMP

CLASS COVER BUMP ;

FOREIGN BUMP -49.45 -49.45 ;

ORIGIN 49.45 49.45 ;

SIZE 98.9 BY 98.9 ;

PIN PAD

DIRECTION INOUT ;

USE SIGNAL ;

PORT

LAYER AP ;

#RECT -49.45 -49.45 49.45 49.45 ;

POLYGON -20.49 -49.45 20.49 -49.45 49.45 -20.49 49.45 20.49 20.49 49.45 -20.49 49.45 -49.45 20.49 -49.45 -20.49 ;

END

END PAD

END BUMPEND LIBRARY

First, create a file called bump.padfile. This file contains one line, the MACRO name of the bump from the LEF. It should look like this:

BUMP

Next, create a file called bump.srcfile. It should look like this:

CELL BUMP

NET PAD

PORT {

AP -49.45 -49.45 49.45 49.45

}

Make sure the CELL and NET names match your bump LEF. The NET name is the PIN name from the LEF. The port layer name (AP here) is the same layer from the LEF. Remember the commented-out square coordinates that I mentioned in the LEF example above? Here is where that's useful: the coordinates of the PORT shape should be a square that encloses the octagonal bump.

Now, create the bump powergrid view. Here is a sample script, called create_bump_pwrgrid.ss0p81v.tcl:

read_lib -lef tech.lef \

BUMP.lefset_power_library_mode \

-accuracy fast \

-celltype allcells \

-extraction_tech_file cworst.qrcTechFile \

-lef_layermap lef_layer.map \

-generic_power_names {VDD 0.81} \

-generic_ground_names {VSS} \

-input_type pr_lefcharacterize_power_library \

-celllist_file bump.list \

-padvsrcfile bump.srcfile \

-libgen_command_file libgen.inc \

-output_directory fast_bump.ss_0p81v

A few notes about the files referenced in this script:

- The bump.list file just contains the bump name and is actually the same as the bump.padfile.

- For an example of the lef_layer.map file, see my last blog, Five-Minute Tutorial: Create Encounter Power System (EPS) Power-Grid Views For Standard Cells.

- The libgen.inc file looks like this (again, the cell and net name should match the bump LEF):

cell_common_supply_names cell BUMP nets {PAD}

Finally, when running rail analysis, use the bump.padfile in your set_power_pads command. The same padfile can be used for any rail:

set_power_pads \

-net VDD \

-format padcell \

-file bump.padfile

set_power_pads \

-net VSS \

-format padcell \

-file bump.padfile

All bumps will then be recognized as voltage sources, with multiple points inside the bump shape. I hope this has helped simplify your rail analysis flow!

- Kari Summers

Answers to Top 10 Questions on Performing ECOs in EDI System

Applying ECOs to a design can be complex, stressful and error prone so it's important to apply the right tools and flow to implement the changes successfully. EDI System provides multiple ECO flows to physically implement ECOs efficiently and accurately based on your design requirements. And adding a tool such as Encounter Conformal ECO Designer or the Encounter Timing System's MMMC Signoff ECO capability can lead to faster design closure with fewer iterations.

I field many customer questions related to implementing physical ECOs with EDI System. In this blog I provide answers to 10 of the most common questions. Do you have any tips to share on performing ECOs with EDI System? If so, please post it as a comment below.

Thanks,

Brian

1. What's the best place to find details on how to perform ECOs in EDI System?

The EDI System User Guide has a chapter dedicated to ECO Flows (Cadence Online Support access required). It describes several flows depending on whether it is a pre-mask or post-mask ECO, whether the changes are coming from a new Verilog netlist, DEF or ECO file, and whether gate array cells are being used or not. If you are new to ECO flows in EDI System then the ECO Flows chapter is the place to start!

It's worth mentioning here ECOs can be implemented using the super-command ecoDesign or by running each command individually (init_design, ecoDefin, ecoPlace, ...). Both methods are described in the User Guide.

2. What's the difference between a pre-mask and post-mask ECO flow?

A pre-mask ECO is when you are making changes to the design before any masks have been made. With a pre-mask ECO you are free to make changse to any layer thus providing you more freedom to implement the ECO.

A post-mask ECO is when you are making changes to a design after masks have been made. Therefore, you want to limit the changes to specific layers so you do not need to re-make all the masks. In a post-mask ECO flow you can utilize existing spare cells which where placed in the design to avoid changes to layers Metal1 and below. You can also instruct the router to which layers it can use to perform ECO routing and which must remain frozen.

3. How do I apply changes made in my RTL to the physical design through ECO?

Encounter Conformal ECO Designer is recommended for performing complex ECOs originating from RTL. It interfaces with RTL Compiler and EDI System to perform the logical and physical ECOs while leveraging Conformal's logical equivalency abilities to ensure the ECO was successful for both the front-end and back-end signoff.

4. How does EDI System identify spare cells in a post-mask ECO flow?

Spare cells should have a unique string in their instance name to identify them. Then the command specifySpareGate or ecoDesign -useSpareCells patternName is run to identify the spare instances. For example, if all spare cells have _spare_ in their name then they are identified using:

specifySpareGate -inst *_spare_*

OR

ecoDesign -spareCells *_spare_* ...

Note if you are making manual ECO changes to a netlist and converting a spare cell to a logical instance, it's important to change the instance name. Otherwise, the instance may be identified as a spare cell if a future ECO is performed because it still has the spare cell instance name.

5. How does EDI System identify the changes in the design?

During the ecoDefin step the existing netlist (new netlist) is compared against the original placed and routed design. A summary of differences is output to the log file and a detailed report file is output to the local directory. You can review the report file to see a list of all the differences.

6. How do I use spare cells or gate array cells during placement?

Spare cells are identified using specifySpareGate. Then use the -useSpareCells true option when running ecoPlace to instruct it to swap the unplaced cells with spare cells of the same cell type:

specifySpareGate -inst *_spare_*

ecoPlace -useSpareCells true

Gate array style filler cells can be programmed with metal layers so the poly/diffusion and lower layers are not changed, and only the metal and via layer masks need to be modified. If you are using gate array spare cells the flow depends on the SITE type used by the gate array cells.

If your design has GA Cells which utilize a SITE type (i.e. GACORE) different from normal standard cells (i.e. CORE) then use:

ecoPlace -useGACells GACORE

If your design has GA cells which utilize the same SITE type as standard cells: ecoPlace -useGAFillerCells {List of GAFillerCells}

Reference the User Guide for the complete flow.

7. Is ecoPlace -useSpareCells true timing driven?

ecoPlace will choose the spare cells to minimize wire length but is not timing driven. After ecoPlace you can run ecoSwapSpareCell to relocate an instance to the location of another spare cell of the same type. Alternatively, you can run ecoRemap in place of ecoPlace. ecoRemap is timing driven and automatically analyzes the functionality of the newly added cells and remaps them to available spare cells. The software analyzes the logic and performs changes to improve timing and minimize DRVs.

8. How do I freeze certain metal layers during routing?

In a post-mask ECO Flow run ecoRoute with the -modifyOnlyLayers option to specify which layers it is allowed to modify. For example, to route using only Metal1 through Metal3:

ecoRoute -modifyOnlyLayers 1:3

9. How does ECO routing deal with metal fill?

When performing a post-mask ECO flow, ecoRoute will ignore the metal fill while routing. This will likely cause DRC violations between the ECO routes and metal fill. To fix these violations, run verifyGeometry followed by the the trimMetalFill command. This will cut back the metal fill from the ECO routing to fix the violations.

10. Does EDI System support interactive (maual) ECOs?

Yes, EDI System provides a number of interactive commands to both evaluate and commit ECO changes. See the Interactive ECO chapter of the EDI System User Guide for details.

When performing interactive ECOs make sure setEcoMode is set as desired. Here are some specific options to pay attention to and tips to speed up run time when implementing a series of ECOs:

setEcoMode -updateTiming - Default is false allowing you to wait until all ECOs are performed to run timing analysis. If set to true, timing analysis is run after each ECO command.

setEcoMode -honorDontTouch, -honorDontUse, -honorFixedStatus - The default for all of these is true. So if you find you cannot make a change, check if any of these apply.

setEcoMode -batchMode - Sets this to true to improve runtime if you are performing many ECOs.

Five-Minute Tutorial: EM Model Files Revisited

11 Things I Learned by Browsing Cadence Online Support

I guess by now most of us are already familiar with Rapid Adoption Kits (RAKs). These are packages that include a detailed instructional document and a lab database. You can browse all the available materials at http://support.cadence.com.

Rapid Adoption Kits (RAKs) - The purpose of RAKs is to demonstrate how users can use Cadence tools in their design flows to improve productivity and to maximize the benefits of their tools. Here are a few important RAKs and appnotes that were published recently on the support portal (http://support.cadence.com) which might be of interest to many of us!

1. RAK - Prototyping Foundation Flat Flow EDI 13.2This content helps us learn gigascale prototyping with FlexModels and presents a prototyping usage model. FlexModels enable gigascale design exploration using the Encounter Digital Implementation (EDI) System.

2. RAK - Introduction to EDI System 13.2 & Block Implementation Flow

This RAK can be extremely helpful for beginners who intend to learn the EDI System. RAK includes EDI command and graphical user interface (GUI), how to set up the EDI system, and how to implement the flat flow that can be used for chip or block Implementation

3. RAK - Basic Floorplanning in EDI System 13.2

This knowledge piece helps us learn how to specify the floorplan, move and edit placement constraints, create placement and routing blockages, create power and ground rings and stripes, and power routing

4. RAK - Power and Rail Analysis Using Encounter Power System (EPS) 13.1

This material provides information on to know how to do library characterization, analyze VCD files for windows of high signal activity, do static and dynamic power analysis, analyze current/power plots, perform what-if analysis & analyze various rail analysis plots

5. Appnote - Time Budgeting for Very Large, Timing Critical Hierarchical Design Using ART Methodology

Time budgeting for very large timing-critical designs using virtual optimization is not accurate enough. With design sizes growing to over 300 million instances, obtaining accurate time budgets with better accuracy for timing critical design is becoming a necessity for many design teams. This document crisply describes how to obtain accurate time budgets using Active-Logic Reduction Technology (ART) to reduce run-time and memory footprint on timing critical designs. This should help the user achieve accurate timing budgets.

6. Appnote - Constraint Implementation and Validation in Interoperability Flow

The key benefit designers derive by using a mixed signal Interoperability flow and OpenAccess (OA) database is the seamless transfer and implementation of various routing constraints from analog to digital designs. Starting from Encounter Digital Implementation (EDI) 13.2 and Virtuoso 616, it is not only simple to create these constraints, but it is also easy to import or export them from one environment to another. Once the design is implemented using these constraints, you can use the Physical Verification System-Constraint Validation (PVS-CV) utility to validate whether these constraints are implemented correctly.

7. Appnote - Context Aware Placement in EDI SystemThis document is targeted to users who want to apply context constraint for cells with Encounter Digital Implementation System (EDI System). It will introduce how to define edge types and the requested spacing rules, how to assign the specified edge types to cells, and how to spread cells with specific edge types to satisfy the spacing rules. It includes recommendations for a successful chip implementation.

8. Appnote - How to Detect and Fix Isolated Cut Via Violations

This content is meant for users and designers needing to locate and fix isolated cut violations in their designs, and CAD engineers wishing to implement such a flow using the Encounter Digital Implementation (EDI) system. This document provides some background to the problem, and a methodology for resolving violations by inserting multi-cut vias.

9. Appnote - Current Mode Virtual Attacker

Modeling small attackers accurately and efficiently is an important factor in the accuracy of noise and noise-on-delay analysis. This application note explains how the current mode virtual attacker is formed and used.

10. Appnote - End Cap Cells Usage in Encounter Digital Implementation (EDI) System FlowIf you want to insert end caps into the design with Encounter Digital Implementation System, this content should help you achieve your goal. It will introduce you to various end cap insertion and verification methodologies recommendations from Cadence for a successful chip implementation.

11. Appnote - Path Exception Priority RulesThis document describes the path exception priority rules which are followed by Encounter Timing System (ETS) / Encounter Digital Implementation (EDI) System for finding effective path exception for a path, among the multiple path exceptions specified for that path. Path exception priority rules are explained (in descending order) as per path exception command type and various command options.

Happy Learning !!

Mukesh Jaiswal

Five-Minute Tutorial: Start the New Year with Voltus

- licensing info

- how to start the tool

- pointers to translation utilities for your existing scripts

- an explanation of the new power grid library view types and how they are used (there used to be 8 different kinds, now there are only 3 - much better!)

- power grid library generation

- static power analysis

- static rail analysis

- dynamic power analysis

- dynamic rail analysis

- vectorless and vector-based analysis

- how to look at results in report files, plots, graphs, etc.

Sharing is Learning - New RAKs and Videos for Digital Users on Cadence Support

Friends, you would probably agree that sharing knowledge is a practical way to solve business problems, and contributes to business goals. Thought I'd share some great content that I came across while navigating through http://support.cadence.com

Rapid Adoption Kits:

Static Timing Analysis using Tempus (Signoff Timing Analysis) 13.2

With the help of this RAK (rapid adoption kit) you will learn how to perform static timing analysis on a dual-tone multi-frequency (DTMF) design using Cadence Tempus Timing Signoff Solution in each of the four modes shown below:

Tempus STA Single Mode Single Corner SMSC

Tempus STA Distributed Multi-Mode Multi-Corner DMMMC

Tempus STA Concurrent Multi-Mode Multi-Corner CMMMC

Tempus DSTA Distributed STA on multiple clients Tempus DSTA

You will be able to:

• Understand how to set up and run each of the Tempus Timing Signoff Solution methods

• Report and analyze static timing results

• Be confident on how to start your new design and choose the methods that are best for you

Timing Signoff Optimization (TSO) using TEMPUS 13.2 & EDI System 13.2

In this RAK, you will learn how to perform ECOs (engineering change orders) for solving hold, setup, and DRV timing violations on a dual-tone multi-frequency (DTMF) design using Tempus Timing Signoff Solution and Cadence Encounter Digital Implementation System.

First section of this will cover Tempus TSO fixing on a block-level design and the subsequent will cover hierarchical chip finishing using Tempus TSO.

This will help to:

• Explain how to investigate timing in an signoff STA environment

• Understand and explain the timing ECO methodology

• Understand and perform all the steps required before starting the ECO process

• Perform hold, setup, and DRV timing fixes through ECOs

• Report and analyze ECO results

• Implement the ECOs in Encounter Digital Implementation System

• Verify final signoff STA

• Assemble a hierarchical design in Tempus Timing Signoff Solution for STA and ECO fixing

• Perform hierarchically aware chip finishing with timing ECOs

• Optimize timing in replicated modules (master/clone)

Videos:

Demo on Implementing Hierarchical Design Using EDI System

This knowledge resource is meant for beginners, new users of EDI System, or users new to the digital implementation design flow. This will help users to learn steps needed in specifying the partitions, creating power and ground rings, running placement and trial/route, assigning partition pins, deriving timing budgets, committing the partitions, pushing into the partitions, and, finally, saving the partitions.

How to create and use ILM (Interface Logic Model) in EDI system

This video showcases steps required in creating the ILMs of a partitioned block, implementation of created ILMs at the top level, and checking of interface logic at the top level of the specified ILM and viewing path, penetrating into the block up to interface logic of the path.

Hope you find these knowledge resources useful.

Happy Learning!

Mukesh Jaiswal

New Training Class: Get Up to Speed Fast When Migrating to Encounter Digital Implementation System

One question we often hear from experienced physical design engineers migrating to Encounter Digital Implementation System is, "How do I get up to speed on the tool as quickly as possible?" They understand place-and-route (P&R) concepts so they often don't need to attend a full training class over several days.

Frequently, they may utilize Rapid Adoption Kits (RAKs), documentation, and other material on Cadence Online Support in an ad hoc way to learn what they need, but that may not be efficient.

To meet this need the Cadence Education Services team recently released the Migration to Encounter Digital Implementation System training class.

If you are a place-and-route (P&R) engineer who needs to quickly migrate to Encounter Digital Implementation System, this is the course for you. The course emphasizes the main features of the Encounter Digital Implementation System while leveraging your prior knowledge of P&R tools to quickly get you productive with the Encounter tool. The class quickly familiarizes you with the Encounter system and its features using lectures and tool demos which you can then apply to your own design. For hands-on experience, the class provides Encounter Digital Implementation (EDI) System and Sign-off Flow RAKs (Cadene Online Support account required to access). For details about the content of the Migration to Encounter Digital Implementation System online class, click here.

I recently discussed this new class with the course developer, Vinita Nelson, to learn more about it.

Q. Vinita, who is the target audience for this class?

A. The target audience for the class would be place-and-route (P&R) engineers or anyone with prior experience running P&R tools and who has a need to migrate to Encounter Digital Implementation System as fast as possible.

Q. How does this class differ from the traditional Encounter Digital Implementation System training class?

A. The Encounter Digital Implementation (Block) course is a three-day course and does not expect prior knowledge in P&R. It's a more traditional nuts-and-bolts course with a lot of detail, whereas the Migration to EDI System course emphasizes core parts of the tool that are unique to the Encounter tool and does not go into as much depth into as many commands and options as the EDI Block tool does. Also, the EDI (Block) course covers topics that are not covered in the Migration course such as ECO, Database Commands and the Foundation Flow (to name a few).

[To view the details of the Encounter Digital Implementation (Block) course, click here.]

Q. How long does it take to complete the course?

A. The online lecture and demo course takes about four hours. The hands-on part could be either downloaded RAKs or the customer's design and those times are variable.

Q. Where can interested users go to find out more or sign up for the class?

A. You can sign up for the class by going to the Cadence website under Training.

[ Go here and click Register]

Brian Wallace

Five-Minute Tutorial: One More Look at EM Models

Just when you thought you were done setting up EM model files, along came another advanced node with more complicated rules. Sound familiar? I've already posted two Five-Minute Tutorials about EM Model File creation—you can review them here and here—but I need to post one more.

In the more recent of the two previous posts, we ended up having to do some hand-editing. Raise your hand if you like to hand-edit important files and feel the fear of an error-prone human process... no one? I didn't think so. Luckily, two of my colleagues (thanks Anton Dvorak and Po-Kai Chen!) showed me a better way than what I detailed for you last time. (As an aside, I apologize for not getting this out sooner. It's been a busy year, and in our line of work, busy is good, so I hope all of you have been very busy as well.)

You may recall from reviewing the previous posts that this method is specific to TSMC and you need to request the iRCX data for your process. That will include a file named something like IRCX_28NM_8M_typical.ircx (use the appropriate extraction corner for the power analysis you plan to run). I'll use this typical filename in the examples below. You also need the qrcTechFile and .ict files that should have come with your extraction data.

Make sure you're using an extraction version of 12.11 or newer. To locate your extraction installation, type:

> which qrc

/apps/EXT141/14.12.000/tools/bin/qrc

Now, you'll run the translator that converts the iRCX file into the .ict format:

>/apps/EXT141/14.12.000/tools/bin/ircxtoict -i new_ict_with_em_info.typical.ict -em_update original.typical.ict IRCX_28NM_8M_typical.ircx

Make a copy of your qrcTechFile (so we don't mess up anything for timing). This step may not be necessary, but I don't like it when the timing guys get mad at me. You can do your own experiments to see if it matters or not.

>cp typical.qrcTechFile EM.typical.qrcTechFile

If you have extraction installed, you have access to Techgen, but just for reference, it can be found in the same install path as the ircxtoict translator. Note the capital "T" at the start of the command. This one is case-sensitive.

Merge the EM info with your qrcTechFile:

>Techgen –update_process EM.typical.qrcTechFile new_ict_with_em_info.typical.ict

Then use the new qrcTechFile in your set_rail_analysis_mode command:

set_rail_analysis_mode -process_techgen_em_rules true -extraction_tech_file EM.typical.qrcTechFile

I hope this has made your EM model file creation easier. I'm also hoping this will be the last EM model blog post for a while, but you never know... 10nm is on the horizon, and I bet that will have some fun surprises!

- Kari Summers

Five-Minute Tutorial: Inserting Column Power Switches in EDI

Hello my fellow Digital Designers,

I'm sorry I haven't been around the blogs much lately. We've had a lot of exciting design work going on that has kept me pretty busy. I hope all of you are having a great 2015 so far. Just a heads up - all links below require a Cadence Online Support account.

Our Educational Services team has been busy putting together some short videos called Training Bytes. These are excerpts from full classes and could certainly fall under the Five-Minute Tutorial category. Today's topic covers how to insert power switch columns into a shut-off domain. More and more designs these days are taking advantage of multiple low-power techniques, and power shut-off is a popular one. EDI offers a lot of flexibility for different power switch methods - in fact, I think the command "addPowerSwitch" should win an award for having the most command options. Seriously, check it out in the EDI System Text Command Reference sometime!

What I like about this Training Bytes video is that it drills down to the basics, using the GUI, to get you going quickly with the most common settings. Starting from scratch with the text command is quite a daunting task, so I expect this video to come in handy for a lot of people. Enjoy the video below, and stay tuned to this blog for more Training Bytes videos in the future!

- Kari Summers

Five-Minute Tutorial: Innovus User Interface Tips

Hi Everyone,

No doubt by now you have heard about the Innovus Implementation System, our next-generation physical implementation solution. It's always a bit scary to move to a new tool, but let me assure you that if you are a current Encounter user, you will be able to get around just fine in the Innovus system. A lot of the user interface will look very familiar to you, but there are some important changes and improvements. (My favorite new feature: tabs!)

Here is a Training Bytes video that highlights some of the UI changes that you'll want to know about. (You'll need an active account on support.cadence.com to view the video.)

What new feature about the Innovus Implementation System, UI or otherwise, excites you? Let me know in the comments. Happy designing!

- Kari Summers

Five-Minute Tutorial: The Innovus Standard Flow

Hi Everyone,

Last week I highlighted a video featuring Innovus User Interface Tips. Now that you know how to get around, what next? Innovus has a new, more streamlined design flow. Most designs should start with what's called the Standard Flow. There is a great document on support.cadence.com outlining this flow. I found it very interesting, and I can't wait to try it on my next design. You'll need an active support.cadence.com account to access the document, which you can find here:

Obviously every design has unique requirements and each design's flow will need a bit of tweaking. But if you are upgrading from Encounter to Innovus, it's important to understand the differences in the new flow and not carry any legacy settings along until you are sure you need them. I, for one, really like the idea of starting out with a fresh, basic design flow so that I can take full advantage of all that Innovus has to offer.

Kari Summers

Five-Minute Tutorial: Innovus Placement Optimization

Hi Everyone,

Last time we got a quick look at The Innovus Standard Flow. Now I'd like to show you a bit more detail about some of the major steps. One of the new concepts in Innovus is how placement and pre-CTS timing optimization are now combined and interleaved. The GigaPlace placement engine is also new, and you will learn about its features. Click below to play the video (you'll need an active support.cadence.com account):

Let's have a big round of applause for long-time Cadence employee Vinita Nelson, our video superstar! I know I've been learning a lot from these Training Bytes, and I hope all of you have been also. Stay tuned to this blog for more Training Bytes featuring the new Innovus flow!

Kari Summers

Five-Minute Tutorial: Innovus Clock Tree Synthesis and Debugger

Hi Everyone,

Last time, our Five-Minute Tutorial focused on the new Innovus Placement Optimization. The next step in the flow would be inserting clock trees. Now that we can take advantage of the CCOpt engine to create clock trees, we can also concurrently optimize for timing. But you still have the choice of whether or not to do so. This is a decision that could be design-dependent, and you may want to try both methods and compare the results. In either case, once clock trees have been created, you may need to do some investigation and/or debugging depending on the results. The Clock Tree Debugger comes in very handy here. This Training Bytes video gives a quick overview of the Clock Tree Synthesis flow as well as the use of the Clock Tree Debugger. Never having used the debugger before, I really learned a lot from this one. (As always, you'll need an active support.cadence.com account to view.)

- Kari Summers